SEESEND วงจรรวมอิเล็กทรอนิกส์ส่วนประกอบเดิมและใหม่ XC2VP50-6FF1152I

คุณสมบัติของผลิตภัณฑ์

| พิมพ์ | คำอธิบาย |

| หมวดหมู่ | วงจรรวม (IC) |

| นาย | เอเอ็มดี ซีลินซ์ |

| ชุด | Virtex®-II Pro |

| บรรจุุภัณฑ์ | ถาด |

| สถานะสินค้า | ล้าสมัย |

| จำนวนห้องปฏิบัติการ/CLB | 5904 |

| จำนวนองค์ประกอบลอจิก/เซลล์ | 53136 |

| บิต RAM ทั้งหมด | 4276224 |

| จำนวน I/O | 692 |

| แรงดันไฟฟ้า – อุปทาน | 1.425V ~ 1.575V |

| ประเภทการติดตั้ง | ติดพื้นผิว |

| อุณหภูมิในการทำงาน | -40°C ~ 100°C (ทีเจ) |

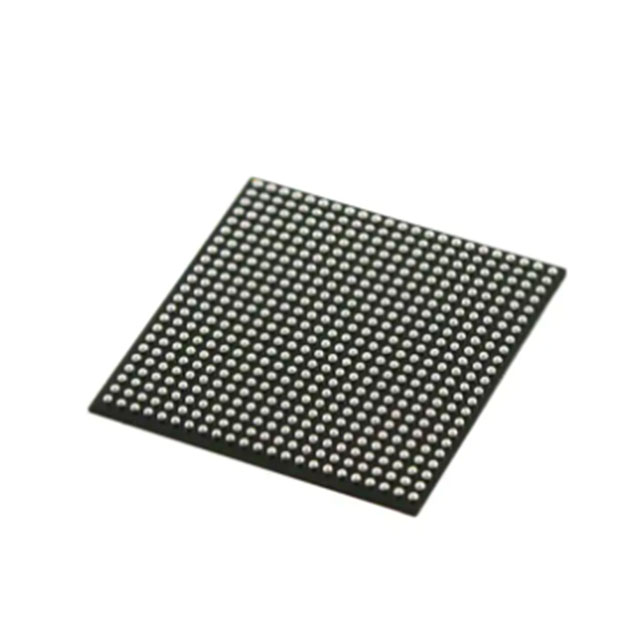

| แพ็คเกจ/กล่อง | 1152-บีบีจีเอ, FCBGA |

| แพคเกจอุปกรณ์ของซัพพลายเออร์ | 1152-FCBGA (35×35) |

| หมายเลขผลิตภัณฑ์ฐาน | XC2VP50 |

เอกสารและสื่อ

| ประเภททรัพยากร | ลิงค์ |

| แผ่นข้อมูล | Virtex-II Pro, Pro X |

| ข้อมูลด้านสิ่งแวดล้อม | ใบรับรอง RoHS ของ Xiliinx |

| PCN ล้าสมัย/EOL | Mult Dev EOL 6/ม.ค./2020 |

| เอกสารข้อมูล HTML | Virtex-II Pro, Pro X |

| โมเดล EDA | XC2VP50-6FF1152I โดย Ultra Librarian |

การจำแนกประเภทสิ่งแวดล้อมและการส่งออก

| คุณลักษณะ | คำอธิบาย |

| สถานะ RoHS | ไม่เป็นไปตาม RoHS |

| ระดับความไวต่อความชื้น (MSL) | 4 (72 ชั่วโมง) |

| สถานะการเข้าถึง | REACH ไม่ได้รับผลกระทบ |

| ECCN | 3A991D |

| เอชทีเอส | 8542.39.0001 |

ภาพรวม XC2VP50-6FF1152I FPGA

กลุ่มผลิตภัณฑ์ Virtex-II Pro และ Virtex-II Pro X มีแพลตฟอร์ม FPGA สำหรับการออกแบบที่ใช้แกน IP และโมดูลที่ปรับแต่งเองXC2VP50-6FF1152I รวมตัวรับส่งสัญญาณหลายกิกะบิตและบล็อก CPU PowerPC ในสถาปัตยกรรม FPGA ซีรีส์ Virtex-II Proช่วยเพิ่มศักยภาพให้กับโซลูชันที่สมบูรณ์สำหรับแอปพลิเคชันโทรคมนาคม ไร้สาย เครือข่าย วิดีโอ และ DSP

กระบวนการทองแดงเก้าชั้น CMOS ระดับชั้นนำ 0.13 µm และสถาปัตยกรรม Virtex-II Pro ได้รับการปรับให้เหมาะสมสำหรับการออกแบบประสิทธิภาพสูงในช่วงความหนาแน่นที่หลากหลายเมื่อรวมคุณลักษณะที่ยืดหยุ่นและคอร์ IP ที่หลากหลาย XC2VP50-6FF1152I ช่วยเพิ่มความสามารถในการออกแบบลอจิกที่ตั้งโปรแกรมได้ และเป็นทางเลือกที่มีประสิทธิภาพแทนอาร์เรย์เกตที่ตั้งโปรแกรมไว้แบบมาส์ก

ซีรีส์ส่วนประกอบ Xilinx Industrial XC2VP50-6FF1152I คือ 53136 Logic Cells 16 Rocket IOs 2 พลัง ดูสิ่งทดแทนและทางเลือก พร้อมด้วยเอกสารข้อมูล สต็อก ราคาจากผู้จัดจำหน่ายที่ได้รับอนุญาตที่ FPGAkey.com และคุณยังสามารถค้นหาผลิตภัณฑ์ FPGA อื่นๆ ได้อีกด้วย

คุณสมบัติ

โซลูชัน FPGA แพลตฟอร์มประสิทธิภาพสูง รวมถึง

ตัวรับส่งสัญญาณหลายกิกะบิต (MGT) แบบฝัง RocketIO หรือ RocketIO X สูงสุดยี่สิบตัว

บล็อกตัวประมวลผล IBM PowerPC RISC สูงสุดสองบล็อก

ใช้เทคโนโลยี FPGA แพลตฟอร์ม Virtex-II

ทรัพยากรลอจิกที่ยืดหยุ่น

การกำหนดค่าในระบบที่ใช้ SRAM

เทคโนโลยีการเชื่อมต่อระหว่างกันแบบแอคทีฟ

เลือกลำดับชั้นหน่วยความจำ RAM+

บล็อกตัวคูณเฉพาะ 18 บิต x 18 บิต

วงจรการจัดการนาฬิกาประสิทธิภาพสูง

เทคโนโลยี SelectI/O-Ultra

XCITE ควบคุมอิมพีแดนซ์แบบดิจิทัล (DCI) I/O