บริการครบวงจร SON8 TPS7A8101QDRBRQ1 พร้อมชิป IC Electronics ดั้งเดิมและใหม่

คุณสมบัติของผลิตภัณฑ์

| พิมพ์ | คำอธิบาย |

| หมวดหมู่ | วงจรรวม (IC) |

| นาย | เท็กซัส อินสทรูเมนท์ส |

| ชุด | ยานยนต์ AEC-Q100 |

| บรรจุุภัณฑ์ | เทปและรีล (TR) เทปตัด (CT) ดิจิ-รีล® |

| SPQ | 3000 ทีแอนด์อาร์ |

| สถานะสินค้า | คล่องแคล่ว |

| การกำหนดค่าเอาต์พุต | เชิงบวก |

| ประเภทเอาต์พุต | ปรับได้ |

| จำนวนหน่วยงานกำกับดูแล | 1 |

| แรงดันไฟฟ้า - อินพุต (สูงสุด) | 6.5V |

| แรงดันไฟฟ้า - เอาท์พุต (ต่ำสุด/คงที่) | 0.8V |

| แรงดันไฟฟ้า - เอาท์พุต (สูงสุด) | 6V |

| แรงดันไฟฟ้าตกคร่อม (สูงสุด) | 0.5V@1A |

| ปัจจุบัน - เอาท์พุต | 1A |

| ปัจจุบัน - นิ่ง (Iq) | 100 ไมโครเอ |

| ปัจจุบัน - อุปทาน (สูงสุด) | 350 ไมโครเอ |

| สสส | 48dB ~ 38dB (100Hz ~ 1MHz) |

| คุณสมบัติการควบคุม | เปิดใช้งาน |

| คุณสมบัติการป้องกัน | กระแสไฟเกิน, อุณหภูมิเกิน, ขั้วย้อนกลับ, การล็อคแรงดันไฟต่ำ (UVLO) |

| อุณหภูมิในการทำงาน | -40°C ~ 125°C (ทีเจ) |

| ประเภทการติดตั้ง | ติดพื้นผิว |

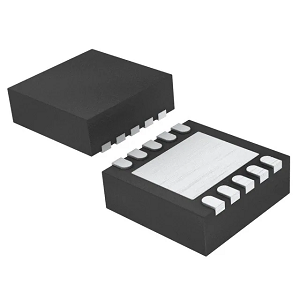

| แพ็คเกจ/กล่อง | 8-VDFN แผ่นสัมผัส |

| แพคเกจอุปกรณ์ของซัพพลายเออร์ | 8-SON (3x3) |

| หมายเลขผลิตภัณฑ์ฐาน | TPS7A8101 |

LDO หรือตัวควบคุมการตกคร่อมต่ำคือตัวควบคุมเชิงเส้นการตกคร่อมต่ำที่ใช้ทรานซิสเตอร์หรือท่อเอฟเฟกต์สนาม (FET) ที่ทำงานในพื้นที่อิ่มตัวเพื่อลบแรงดันไฟฟ้าส่วนเกินออกจากแรงดันไฟฟ้าอินพุตที่ใช้เพื่อสร้างแรงดันเอาต์พุตที่มีการควบคุม

องค์ประกอบหลักสี่ประการ ได้แก่ การออกกลางคัน เสียง อัตราส่วนการปฏิเสธแหล่งจ่ายไฟ (PSRR) และ Iq กระแสนิ่ง

ส่วนประกอบหลัก: วงจรเริ่มต้น, หน่วยไบอัสของแหล่งจ่ายกระแสคงที่, วงจรเปิดใช้งาน, องค์ประกอบการปรับ, แหล่งอ้างอิง, เครื่องขยายสัญญาณข้อผิดพลาด, เครือข่ายตัวต้านทานป้อนกลับและวงจรป้องกัน ฯลฯ

หลักการทำงาน

วงจรพื้นฐานของ LDO ประกอบด้วยชุดควบคุม VT, ตัวต้านทานการสุ่มตัวอย่าง R1 และ R2 และแอมพลิฟายเออร์เปรียบเทียบ A

ระบบถูกขับเคลื่อน หากพินเปิดใช้งานอยู่ที่ระดับสูง วงจรจะเริ่มทำงาน วงจรแหล่งจ่ายกระแสคงที่จะให้ไบแอสกับวงจรทั้งหมด แรงดันไฟฟ้าแหล่งอ้างอิงจะถูกสร้างขึ้นอย่างรวดเร็ว และใช้แรงดันไฟฟ้าอินพุตที่ไม่ได้รับการควบคุมเป็นแรงดันไฟฟ้า ของแหล่งจ่ายไฟ แรงดันอ้างอิงถูกใช้เป็นแรงดันไฟฟ้าอินพุตเฟสลบของเครื่องขยายข้อผิดพลาด เครือข่ายป้อนกลับตัวต้านทานจะแบ่งแรงดันเอาต์พุตและรับแรงดันป้อนกลับ แรงดันป้อนกลับนี้จะถูกป้อนเข้าไปยังขั้วทิศทางเดียวกันของตัวเปรียบเทียบข้อผิดพลาด และค่าลบ แรงดันป้อนกลับนี้จะถูกป้อนเข้าที่ด้านไอโซโทรปิกของตัวเปรียบเทียบข้อผิดพลาด และเปรียบเทียบกับแรงดันอ้างอิงค่าลบความแตกต่างระหว่างแรงดันไฟฟ้าทั้งสองจะถูกขยายโดยตัวขยายข้อผิดพลาดเพื่อควบคุมประตูขององค์ประกอบปรับกำลังโดยตรง และเอาต์พุตของ LDO จะถูกควบคุมโดยการเปลี่ยนสถานะการนำไฟฟ้าของท่อปรับ เช่น Vout = (R1 + R2)/ R2 × เวอเรฟ

ตัวควบคุมเชิงเส้นตกคร่อมต่ำจริงยังมีฟังก์ชันอื่น ๆ เช่นการป้องกันการลัดวงจรของโหลด การปิดระบบแรงดันไฟฟ้าเกิน การปิดระบบด้วยความร้อน การป้องกันการเชื่อมต่อแบบย้อนกลับ ฯลฯ

ข้อดีข้อเสียและสถานะปัจจุบัน

ตัวควบคุมเชิงเส้นแรงดันไฟฟ้าตกคร่อมต่ำ (LDO) มีต้นทุนต่ำ สัญญาณรบกวนต่ำ กระแสไฟนิ่งต่ำ มีส่วนประกอบภายนอกเพียงไม่กี่ตัว โดยปกติจะมีตัวเก็บประจุบายพาสเพียงหนึ่งหรือสองตัวเท่านั้น และมีสัญญาณรบกวนของตัวเองต่ำมากและมีอัตราส่วนการปฏิเสธแหล่งจ่ายไฟ (PSRR) สูงLDO เป็นระบบบนชิป (SoC) ขนาดเล็กที่มีการสิ้นเปลืองพลังงานเองต่ำมากสามารถใช้สำหรับการควบคุมช่องสัญญาณหลักในปัจจุบัน และมีวงจรฮาร์ดแวร์ในตัว เช่น MOSFET ที่มีความต้านทานออนไลน์อินไลน์ต่ำมาก ไดโอด Schottky ตัวต้านทานการสุ่มตัวอย่าง และตัวแบ่งแรงดันไฟฟ้า รวมถึงการป้องกันกระแสไฟเกิน การป้องกันอุณหภูมิเกิน แหล่งอ้างอิงที่แม่นยำ แอมพลิฟายเออร์ดิฟเฟอเรนเชียล ตัวดีเลย์ ฯลฯ PG คือ LDO รุ่นใหม่ที่มีการทดสอบตัวเองสำหรับแต่ละสถานะเอาต์พุตและแหล่งจ่ายไฟที่ปลอดภัยแบบหน่วงเวลา ซึ่งสามารถเรียกอีกอย่างว่า Power Good กล่าวคือ "กำลังดีหรือกำลังเสถียร" .LDO จำนวนมากต้องการตัวเก็บประจุเพียงตัวเดียวที่อินพุตและอีกตัวที่เอาต์พุตเพื่อการทำงานที่เสถียร

LDO ใหม่สามารถบรรลุข้อกำหนดต่อไปนี้: สัญญาณรบกวนเอาท์พุตที่ 30µV, PSRR ที่ 60dB, กระแสนิ่งที่ 6µA และแรงดันไฟฟ้าตกเพียง 100mVเหตุผลหลักสำหรับประสิทธิภาพที่ดีขึ้นของตัวควบคุมเชิงเส้น LDO คือตัวควบคุมที่ใช้คือ P-channel MOSFET ซึ่งขับเคลื่อนด้วยแรงดันไฟฟ้าและไม่ต้องใช้กระแสไฟฟ้า ช่วยลดกระแสที่ใช้โดยตัวอุปกรณ์เองและแรงดันไฟฟ้าตกคร่อมอุปกรณ์การปล่อยจะเท่ากับผลคูณของกระแสเอาต์พุตและความต้านทานออนโดยประมาณแรงดันไฟฟ้าตกคร่อม MOSFET ต่ำมากเนื่องจากมีความต้านทานออนต่ำตัวควบคุมเชิงเส้นทั่วไปใช้ทรานซิสเตอร์ PNPในวงจรที่มีทรานซิสเตอร์ PNP แรงดันไฟฟ้าตกระหว่างอินพุตและเอาต์พุตจะต้องไม่ต่ำเกินไป เพื่อป้องกันไม่ให้ทรานซิสเตอร์ PNP เข้าสู่ภาวะอิ่มตัวและลดความสามารถของเอาต์พุต

.png)

-300x300.png)