ชิป ic อิเล็กทรอนิกส์รองรับบริการ BOM TPS54560BDDAR ชิป ic ใหม่ล่าสุดส่วนประกอบอิเล็กทรอนิกส์

คุณสมบัติของผลิตภัณฑ์

| พิมพ์ | คำอธิบาย |

| หมวดหมู่ | วงจรรวม (IC) |

| นาย | เท็กซัส อินสทรูเมนท์ส |

| ชุด | อีโค-โหมด™ |

| บรรจุุภัณฑ์ | เทปและรีล (TR) เทปตัด (CT) ดิจิ-รีล® |

| SPQ | 2500ทีแอนด์อาร์ |

| สถานะสินค้า | คล่องแคล่ว |

| การทำงาน | หลีกทาง |

| การกำหนดค่าเอาต์พุต | เชิงบวก |

| โทโพโลยี | บั๊ก, รางแยก |

| ประเภทเอาต์พุต | ปรับได้ |

| จำนวนเอาท์พุต | 1 |

| แรงดันไฟฟ้า - อินพุต (ต่ำสุด) | 4.5V |

| แรงดันไฟฟ้า - อินพุต (สูงสุด) | 60V |

| แรงดันไฟฟ้า - เอาท์พุต (ต่ำสุด/คงที่) | 0.8V |

| แรงดันไฟฟ้า - เอาท์พุต (สูงสุด) | 58.8V |

| ปัจจุบัน - เอาท์พุต | 5A |

| ความถี่ - การสลับ | 500กิโลเฮิร์ตซ์ |

| วงจรเรียงกระแสแบบซิงโครนัส | No |

| อุณหภูมิในการทำงาน | -40°C ~ 150°C (ทีเจ) |

| ประเภทการติดตั้ง | ติดพื้นผิว |

| แพ็คเกจ/กล่อง | 8-PowerSOIC (0.154", กว้าง 3.90 มม.) |

| แพคเกจอุปกรณ์ของซัพพลายเออร์ | พาวเวอร์แพด 8-SO |

| หมายเลขผลิตภัณฑ์ฐาน | ทีพีเอส54560 |

1.การตั้งชื่อ IC ความรู้ทั่วไปของแพ็คเกจ และกฎการตั้งชื่อ:

ช่วงอุณหภูมิ

C=0°C ถึง 60°C (เกรดเชิงพาณิชย์);I=-20°C ถึง 85°C (เกรดอุตสาหกรรม);E=-40°C ถึง 85°C (เกรดอุตสาหกรรมแบบขยาย);A=-40°C ถึง 82°C (เกรดการบินและอวกาศ);M=-55°C ถึง 125°C (เกรดทหาร)

ประเภทแพ็คเกจ

A-SSOP;บี-เซอร์ควอด;C-TO-200, TQFP;ท็อปทองแดง D-Ceramic;E-QSOP;F-เซรามิก SOP;H- SBGAJ-เซรามิกกรมทรัพย์สินทางปัญญา;K-TO-3;L-LCC, M-MQFP;N-แคบกรมทรัพย์สินทางปัญญา;เอ็น-กรมทรัพย์สินทางปัญญา;คิว บมจ.;R - DIP เซรามิกแคบ (300mil);S - TO-52, T - TO5, TO-99, TO-100;คุณ - TSSOP, uMAX, SOT;W - ฟอร์มแฟคเตอร์ขนาดเล็กแบบกว้าง (300 ล้าน) ฟอร์มแฟคเตอร์ขนาดเล็กแบบ W-Wide (300 ล้าน);เอ็กซ์-SC-60 (3P, 5P, 6P);ท็อปทองแดง Y-Narrow;Z-TO-92, MQUAD;ดี-ดาย;/PR-พลาสติกเสริมแรง;/W-เวเฟอร์.

จำนวนพิน:

เอ-8;ข-10;ค-12, 192;ง-14;อี-16;เอฟ-22, 256;ก-4;ชั่วโมง-4;ฉัน -4;เอช-4;I-28;เจ-2;เค-5, 68;L-40;ม-6, 48;น 18;O-42;P-20;ควอเตอร์-2, 100;R-3, 843;เอส-4, 80;ที-6, 160;U-60 -6,160;U-60;วี-8 (รอบ);W-10 (รอบ);X-36;Y-8 (รอบ);Z-10 (กลม)(กลม).

หมายเหตุ: ตัวอักษรตัวแรกของส่วนต่อท้ายตัวอักษรสี่ตัวของคลาสอินเทอร์เฟซคือ E ซึ่งหมายความว่าอุปกรณ์มีฟังก์ชันป้องกันไฟฟ้าสถิต

2.การพัฒนาเทคโนโลยีบรรจุภัณฑ์

วงจรรวมยุคแรกสุดใช้แพ็คเกจเซรามิกแบบแบน ซึ่งกองทัพยังคงใช้ต่อไปเป็นเวลาหลายปี เนื่องจากมีความน่าเชื่อถือและขนาดที่เล็กในไม่ช้าบรรจุภัณฑ์วงจรเชิงพาณิชย์ก็เปลี่ยนไปใช้แพ็คเกจอินไลน์คู่ โดยเริ่มจากเซรามิกและพลาสติก และในช่วงปี 1980 จำนวนพินของวงจร VLSI เกินขีดจำกัดการใช้งานของแพ็คเกจ DIP ในที่สุดก็นำไปสู่การเกิดขึ้นของอาร์เรย์พินกริดและตัวพาชิป

แพ็คเกจการติดตั้งบนพื้นผิวเกิดขึ้นในช่วงต้นทศวรรษ 1980 และได้รับความนิยมในช่วงปลายทศวรรษนั้นใช้ระยะพินที่ละเอียดกว่าและมีรูปทรงปีกนกหรือรูปตัว Jตัวอย่างเช่น วงจรรวมโครงร่างขนาดเล็ก (SOIC) มีพื้นที่น้อยกว่า 30-50% และมีความหนาน้อยกว่า DIP ที่เทียบเท่ากัน 70%แพคเกจนี้มีหมุดรูปปีกนกยื่นออกมาจากด้านยาวทั้งสองด้านและมีระยะพิทช์ 0.05 นิ้ว

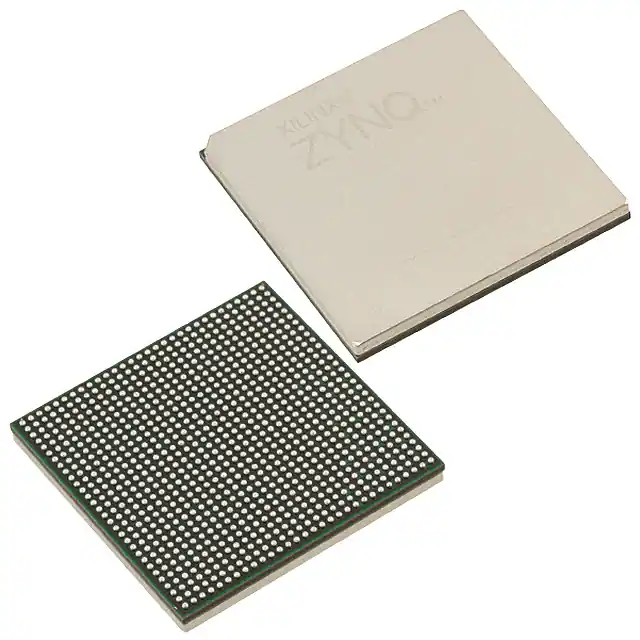

วงจรรวมโครงร่างขนาดเล็ก (SOIC) และแพ็คเกจ PLCCในช่วงทศวรรษ 1990 แม้ว่าแพ็คเกจ PGA มักจะใช้สำหรับไมโครโปรเซสเซอร์ระดับไฮเอนด์ก็ตามPQFP และแพ็คเกจขนาดเล็กบาง (TSOP) กลายเป็นแพ็คเกจปกติสำหรับอุปกรณ์ที่มีจำนวนพินสูงไมโครโปรเซสเซอร์ระดับไฮเอนด์ของ Intel และ AMD ย้ายจากแพ็คเกจ PGA (Pine Grid Array) ไปเป็นแพ็คเกจ Land Grid Array (LGA)

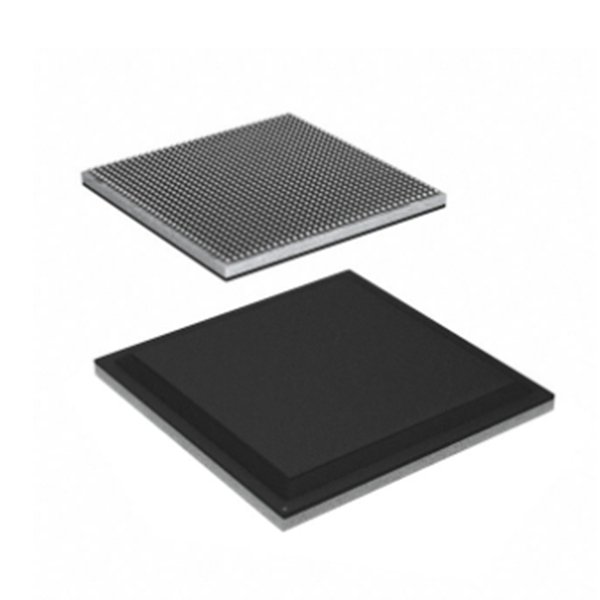

แพ็คเกจ Ball Grid Array เริ่มปรากฏในปี 1970 และในปี 1990 แพ็คเกจ FCBGA ได้รับการพัฒนาโดยมีจำนวนพินที่สูงกว่าแพ็คเกจอื่นๆในแพ็คเกจ FCBGA แม่พิมพ์จะพลิกขึ้นและลงและเชื่อมต่อกับลูกบอลบัดกรีบนแพ็คเกจด้วยชั้นฐานคล้าย PCB แทนที่จะเป็นสายไฟในตลาดปัจจุบัน บรรจุภัณฑ์ก็เป็นส่วนหนึ่งของกระบวนการที่แยกจากกัน และเทคโนโลยีของบรรจุภัณฑ์ก็อาจส่งผลต่อคุณภาพและผลผลิตของผลิตภัณฑ์ได้เช่นกัน