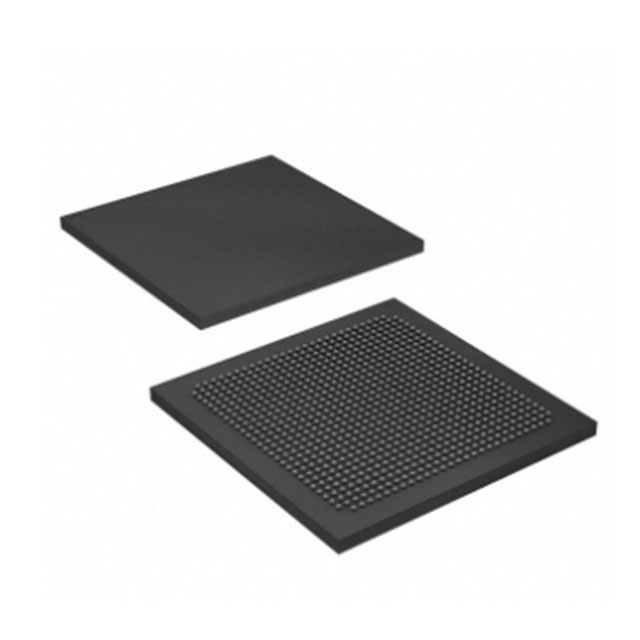

5CEFA5F23I7N Cyclone® VE อาร์เรย์เกตโปรแกรมฟิลด์ได้ (FPGA) IC 240 5001216 77000 484-BGA

คุณสมบัติของผลิตภัณฑ์

| พิมพ์ | แสดงภาพประกอบ |

| หมวดหมู่ | อาร์เรย์เกทที่ตั้งโปรแกรมได้ภาคสนาม (FPGA) |

| ผู้ผลิต | อินเทล |

| ชุด | ไซโคลน® VE |

| ห่อ | ถาด |

| สถานะสินค้า | คล่องแคล่ว |

| DigiKey สามารถตั้งโปรแกรมได้ | ไม่ได้รับการยืนยัน |

| หมายเลขห้องปฏิบัติการ/CLB | 29080 |

| จำนวนองค์ประกอบ/หน่วยตรรกะ | 77000 |

| จำนวนบิต RAM ทั้งหมด | 5001216 |

| I/O | 240 |

| แรงดันไฟฟ้า - แหล่งจ่ายไฟ | 1.07V~1.13V |

| ประเภทการติดตั้ง | ประเภทกาวติดพื้นผิว |

| อุณหภูมิในการทำงาน | -40°C ~ 100°C(ทีเจ) |

| แพ็คเกจ/ที่อยู่อาศัย | 484-บีจีเอ |

| การห่อหุ้มส่วนประกอบของผู้ขาย | 484-FBGA (23x23) |

| หมายเลขหลักผลิตภัณฑ์ | 5CEFA5 |

การแนะนำสินค้า

อุปกรณ์ Cyclone® V ได้รับการออกแบบมาเพื่อรองรับความต้องการพลังงานที่ลดลง ต้นทุน และเวลาในการนำออกสู่ตลาดไปพร้อมๆ กันและความต้องการแบนด์วิธที่เพิ่มขึ้นสำหรับแอปพลิเคชันที่มีปริมาณมากและมีความอ่อนไหวต่อต้นทุนเสริมประสิทธิภาพด้วยตัวรับส่งสัญญาณและตัวควบคุมหน่วยความจำฮาร์ดดิสก์ อุปกรณ์ Cyclone V เหมาะสำหรับการใช้งานในตลาดอุตสาหกรรม ระบบไร้สายและแบบใช้สาย การทหาร และยานยนต์

คุณสมบัติของสินค้า

เทคโนโลยี

- เทคโนโลยีการผลิตพลังงานต่ำ 28 นาโนเมตร (28LP) ของ TSMC

- แรงดันไฟฟ้าหลัก 1.1 V

บรรจุภัณฑ์

- แพ็คเกจฮาโลเจนต่ำแบบ Wirebond

- ความหนาแน่นของอุปกรณ์ที่หลากหลายพร้อมแพ็คเกจที่เข้ากันได้เพื่อการโยกย้ายที่ราบรื่นระหว่างความหนาแน่นของอุปกรณ์ที่แตกต่างกัน

- ตัวเลือกที่สอดคล้องกับ RoHS และตะกั่ว

ผ้า FPGA ประสิทธิภาพสูง

- ALM 8 อินพุตที่ได้รับการปรับปรุงพร้อมรีจิสเตอร์สี่ตัว

บล็อกหน่วยความจำภายใน

- M10K—บล็อกหน่วยความจำ 10 กิโลบิต (Kb) พร้อมรหัสแก้ไขข้อผิดพลาดแบบซอฟต์ (ECC)

- Memory Logic Array Block (MLAB)— LUTRAM แบบกระจาย 640 บิต ซึ่งคุณสามารถใช้ ALM ได้ถึง 25% เป็นหน่วยความจำ MLAB

บล็อก Hard IP แบบฝัง

- รองรับระดับความแม่นยำในการประมวลผลสัญญาณสูงสุดสามระดับ (9 x 9 สามระดับ, 18 x 18 สองระดับ หรือตัวคูณ 27 x 27 หนึ่งตัว) ในบล็อก DSP ที่มีความแม่นยำแปรผันเดียวกัน

- ตัวสะสมและน้ำตกแบบ 64 บิต

- หน่วยความจำสัมประสิทธิ์ภายในที่ฝังอยู่

- เครื่องเตรียม/ตัวลบเพื่อประสิทธิภาพที่ดีขึ้น

- DDR3, DDR2 และ LPDDR2 พร้อมรองรับ ECC 16 และ 32 บิต

- PCI Express* (PCIe*) Gen2 และ Gen1 (x1, x2 หรือ x4) ฮาร์ด IP พร้อมการรองรับมัลติฟังก์ชั่น จุดสิ้นสุด และพอร์ตรูท

การกำหนดค่า

- การป้องกันแอมแปร์—การป้องกันการออกแบบที่ครอบคลุมเพื่อปกป้องการลงทุนด้าน IP อันมีค่าของคุณ

- คุณสมบัติด้านความปลอดภัยการออกแบบมาตรฐานการเข้ารหัสขั้นสูง (AES) ที่ได้รับการปรับปรุง

- ซีวีพี

- การกำหนดค่าใหม่แบบไดนามิกของ FPGA

- ตัวเลือกการกำหนดค่าแบบอนุกรมที่ใช้งานอยู่ (AS) x1 และ x4, แบบพาสซีฟ (PS), JTAG และแบบพาสซีฟแบบพาสซีฟเร็ว (FPP) x8 และ x16

- การขัดภายใน (2)

- การกำหนดค่าใหม่บางส่วน (3)

เขียนข้อความของคุณที่นี่แล้วส่งมาให้เรา